20世纪,发明家们创造了公众日常依赖的设备。可以说,最重要的发明之一是**晶体管**。晶体管于1947年由贝尔实验室的工程师开发,其最初目的是放大电话线上的声音。晶体管取代了更老的技术——真空管。真空管不可靠、体积庞大,并且会产生大量热量。

第一个晶体管是**点接触式晶体管**,高半英寸(1.27厘米)。这个晶体管的功率不大,但物理学家们认识到了该设备的潜力。不久之后,物理学家和工程师开始将晶体管集成到各种电子设备中。随着时间的推移,他们也学会了如何使晶体管更小、更高效。

广告

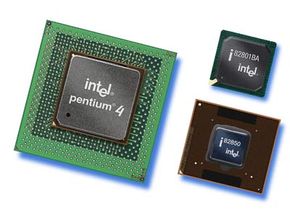

1958年,工程师将两个晶体管连接到硅晶体上,创造了世界上第一个**集成电路**[来源:英特尔]。集成电路的出现为微处理器的发展铺平了道路。如果将计算机比作人类,微处理器就是大脑。它进行计算和处理数据。

到20世纪60年代,计算机科学家(也是英特尔联合创始人)戈登·摩尔提出了一项有趣的观察:他注意到每12个月,工程师们就能使一平方英寸硅片上的晶体管数量翻一番。就像钟表一样,工程师们不断寻找方法来缩小晶体管的尺寸。正是由于这些微小的晶体管,我们才有了个人电脑、智能手机和MP3播放器等电子设备。没有晶体管,我们仍然需要使用真空管和机械开关来进行计算。

自摩尔观察以来,这种小型化趋势仍在继续。但它并未保持摩尔最初观察到的速度。如今,晶体管数量每24个月翻一番。但这引出了一个有趣的问题:晶体管——以及由此延伸的CPU——能做到多小?1947年,单个晶体管的高度略高于百分之一米。到2010年代,英特尔生产的微处理器中的晶体管宽度仅为45纳米。一纳米是十亿分之一米!

英特尔和其他微处理器制造商已经在开发下一代芯片。这些芯片将使用宽度仅为32纳米的晶体管。但一些物理学家和工程师认为,在晶体管尺寸方面,我们可能正在触及一些基本的物理极限。

广告